新書推薦:

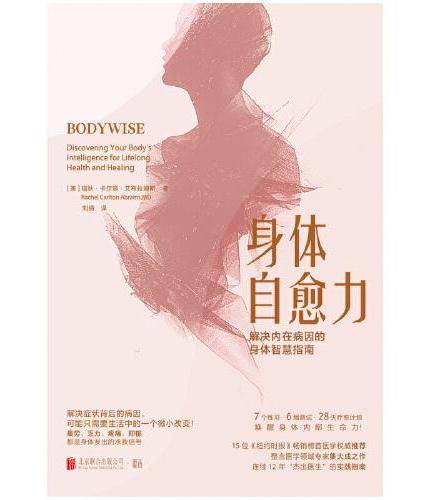

《

身体自愈力:解决内在病因的身体智慧指南

》

售價:HK$

98.6

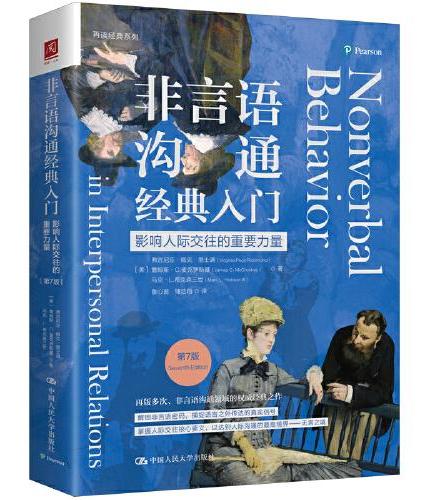

《

非言语沟通经典入门:影响人际交往的重要力量(第7版)

》

售價:HK$

123.1

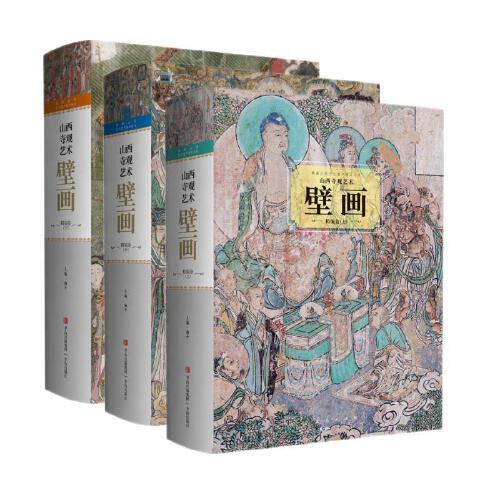

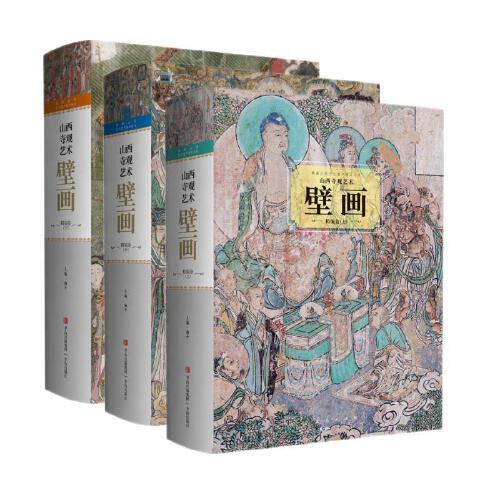

《

山西寺观艺术壁画精编卷

》

售價:HK$

1680.0

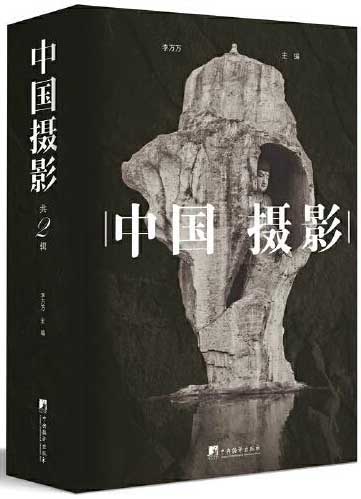

《

中国摄影 中式摄影的独特魅力

》

售價:HK$

1097.6

《

山西寺观艺术彩塑精编卷

》

售價:HK$

1680.0

《

积极心理学

》

售價:HK$

55.8

《

自由,不是放纵

》

售價:HK$

54.9

《

甲骨文丛书·消逝的光明:欧洲国际史,1919—1933年(套装全2册)

》

售價:HK$

277.8

|

| 內容簡介: |

|

本书系统讲解通信网络领域Xilinx FPGA内部的IP硬核。以流行的Xilinx Virtex-6型号芯片举例,涵盖Xilinx FPGA在通信领域主流的IP核,阐述Xilinx FPGA时钟资源和DCM、PLL和MMCM时钟管理器的特性和使用方法;介绍基于Block RAM资源生成ROM、RAM、FIFO和CAM核的使用过程。阐述TEMAC核背景知识、内部结构、接口时序和配置参数,给出生成实例;介绍LVDS技术规范、源同步实现方案和去偏移技术,讲解Xilinx FPGA中IODELAYE1、ISERDES1和OSERDES核使用方法;阐述Xilinx FPGA DDR3控制器IP核的结构组成、模块划分、接口信号和物理约束等。

|

| 關於作者: |

|

黄万伟,博士,江苏盐城人,一直从事网络路由、交换和安全设备的系统设计和硬件开发,在FPGA IP核应用和高速接口设计方面积累了丰富的工程经验,先后撰写学术论文十余篇,申请国家专利6项,多次作为硬件设计负责人承担国家“863”项目和“973”项目,取得了一系列科研成果,多次获得国家和省市级科技进步奖项。长期从事电子类竞赛的指导工作,2012年指导研究生团队取得第八届全国研究生电子设计竞赛一等奖,获得电子学会颁发的优秀指导老师称号。 董永吉,博士,吉林汪清人,一直从事网络安全设备的硬件开发,发表论文十余篇,El收录4篇,申请专利5项,曾作为指导老师在第八届全国研究生电子设计竞赛中荣获一等奖,参与了包括国家“863”项目和“973”项目等在内的多项科研课题的研究。

|

| 目錄:

|

目 录

第1章 Xilinx FPGA发展和应用 1

1.1 可编程器件现状和发展简介 1

1.1.1 可编程器件的特点与应用 1

1.1.2 可编程器件厂家介绍 2

1.1.3 可编程器件发展趋势 4

1.2 Xilinx FPGA简介 4

1.2.1 Xilinx FPGA产品介绍 4

1.2.2 Xilinx Virtex-6系列FPGA 6

1.3 基于IP Core的FPGA设计 7

1.3.1 IP Core分类 8

1.3.2 AXI总线协议在Xilinx IP核中的应用 9

1.3.3 基于IP Core的FPGA设计流程 12

1.4 FPGA在通信领域的应用优势 15

1.4.1 FPGA在通信领域的技术优势 15

1.4.2 Xilinx FPGA的IP核群 15

1.5 NetFPGA板卡的应用基础 16

1.5.1 NetFPGA-1G板卡介绍 16

1.5.2 NetFPGA-10G板卡介绍 17

1.5.3 大学生信息安全竞赛与NetFPGA 18

1.6 本章小结 18

第2章 Xilinx FPGA时钟资源详述 19

2.1 Xilinx FPGA时钟资源 19

2.1.1 Xilinx FPGA时钟资源分类 19

2.1.2 Xilinx FPGA时钟管理器说明 20

2.2 Xilinx FPGA时钟详述 21

2.2.1 时钟相关的基本概念 21

2.2.2 全局时钟资源介绍 23

2.2.3 区域时钟 32

2.3 Virtex-5 DCM介绍与使用说明 38

2.3.1 DCM功能和结构 39

2.3.2 DCM生成演示过程 46

2.3.3 DCM IP核时序仿真 52

2.4 Virtex-5 PLL介绍与使用说明 53

2.4.1 PLL内部结构和功能说明 53

2.4.2 PLL生成演示过程 58

2.4.3 PLL IP核时序仿真 63

2.5 Virtex-6 MMCM介绍与使用说明 64

2.5.1 MMCM功能和结构简介 65

2.5.2 MMCM生成演示过程 73

2.5.3 MMCM IP核时序仿真 79

2.6 本章小结 79

第3章 Block RAM核的功能简介和应用说明 80

3.1 Xilinx FPGA器件内部存储资源介绍 80

3.1.1 基于Block RAM的IP核简介 80

3.1.2 Block RAM与DRAM的区别 84

3.2 Virtex-6 Block RAM内部结构详细说明 84

3.2.1 Block RAM接口介绍 84

3.2.2 Block RAM写属性介绍 87

3.3 ROM核生成实例详解 88

3.3.1 ROM核生成演示 88

3.3.2 coe文件解释说明 93

3.3.3 ROM接口信号时序图 95

3.4 RAM IP核生成实例详解 96

3.4.1 RAM IP核生成演示 96

3.4.2 RAM接口信号时序图 101

3.5 FIFO IP核生成实例详解 101

3.5.1 FIFO IP核生成演示 101

3.5.2 FIFO接口信号时序图 107

3.5.3 FIFO生成命名规范 108

3.6 CAM IP核生成实例详解 109

3.6.1 TCAM器件的相关知识 109

3.6.2 CAM IP核简介 111

3.6.3 CAM IP接口信号说明 113

3.6.4 CAM核工作模式 116

3.6.5 CAM IP核生成演示 121

3.6.6 CAM IP接口信号时序图 125

3.7 本章小结 126

第4章 TEMAC核的功能和应用介绍 127

4.1 以太网技术介绍 127

4.1.1 以太网的发展演进 127

4.1.2 以太网协议规范介绍 129

4.2 Xilinx千兆以太网解决方案 131

4.2.1 千兆以太网IP核简介 132

4.2.2 TEMAC核的典型应用 132

4.2.3 TEMAC核开发优势 133

4.3 TEMAC核结构介绍 133

4.3.1 TEMAC整体结构 134

4.3.2 嵌入式以太网MAC功能简介 135

4.4 用户接口信号详述 137

4.4.1 用户发送接口功能和信号介绍 138

4.4.2 用户接收接口功能和信号介绍 140

4.5 AXI4-Lite接口信号 145

4.5.1 AXI4-Lite接口信号说明 145

4.5.2 基于AXI4-Lite接口的读过程 145

4.5.3 基于AXI4-Lite接口的写过程 147

4.5.4 MAC地址帧内容过滤 148

4.5.5 基于AXI4-Lite接口的相关配置和管理 150

4.6 MDIO配置接口 150

4.6.1 MDIO接口简介 150

4.6.2 MDIO接口信号定义 151

4.6.3 TEMAC核中的MDIO控制 152

4.7 物理接口说明 153

4.7.1 MII接口分析 154

4.7.2 GMIIRGMII接口分析 154

4.7.3 SGMII1000 Base-X接口分析 155

4.8 TEMAC核的生成和仿真实验 156

4.8.1 TEMAC核的生成 156

4.8.2 建立TEMAC核仿真工程 164

4.8.3 TEMAC仿真实验说明 166

4.9 本章小结 170

第5章 LVDS技术规范及其应用 171

5.1 LVDS接口标准和规范 171

5.1.1 LVDS技术规范简介 171

5.1.2 LVDS典型电路简介 172

5.2 LVDS源同步传输方案 174

5.2.1 源同步接口介绍 174

5.2.2 源同步偏斜分析 175

5.2.3 去偏斜解决方案 175

5.3 OIF-SPI4-02.10接口标准 177

5.3.1 SPI-4.2接口简介 177

5.3.2 SPI-4.2接口信号和功能描述 178

5.4 IODELAYE1 IP核说明 183

5.4.1 IODELAYE1概述 183

5.4.2 IODELAYE1接口信号和参数 184

5.4.3 IODELAYE1延迟控制时序 187

5.4.4 IDELAYCTRL的介绍 188

5.5 ISERDESE1 IP核说明 189

5.5.1 ISERDESE1接口和功能概述 189

5.5.2 ISERDESE1的接口信号和属性 190

5.5.3 BITSLIP子模块说明 194

5.6 OSERDES IP核说明 196

5.6.1 OSERDES结构概述 196

5.6.2 OSERDES接口信号和属性 197

5.6.3 OSERDES接口信号时序 200

5.7 动态相位调整解决方案 202

5.7.1 DPA实现方案概述 202

5.7.2 DPA实现简介 203

5.8 本章小结 206

第6章 Xilinx DDR3存储器接口解决方案 207

6.1 DDR3 SDRAM存储器概述 207

6.1.1 DDR3 SDRAM相关名词解释 208

6.1.2 DDR3 SDRAM存储器操作流程 213

6.1.3 DDR3 SDRAM引脚介绍 214

6.2 DDR3控制器IP核主要模块描述 215

6.2.1 用户接口模块 217

6.2.2 存储器控制模块 221

6.2.3 PHY模块 223

6.3 DDR3 IP核接口操作 230

6.3.1 用户接口操作 231

6.3.2 读延迟 236

6.4 DDR3控制器IP核的例化 236

6.4.1 选择MIG工具 236

6.4.2 DDR3控制器的生成 241

6.4.3 DDR3控制器IP核生成文件说明 253

6.4.4 UCF文件校验及规则 254

6.5 DDR3控制器IP核的约束 259

6.5.1 时序约束 259

6.5.2 IO引脚约束 260

6.6 DDR3控制器IP核的仿真模型 261

6.6.1 流量生成器 262

6.6.2 存储器初始化和流量测试 267

6.6.3 仿真调试 268

6.7 本章小结 274

|

|